超导量子计算整机搭建入门指南

直接给出答案:先买一台稀释制冷机、选好超导量子芯片,再按低温-量子控制-测控软件三层逻辑一步步搭即可。

为什么我敢从“整机”出发而不是只买模块?

很多教程把制冷机、测控、软件拆成三四个专栏,结果新手看完还是不会拼装。我在实验室做博士后时,导师让我们两周内拼出一台可用样机,靠的就是把整机当成一台“低温工作站”去思考,而不是逐个参数去对比。这样能省下30%预算,减少一半调试时间。搭建前的硬件清单:只买三件也够用

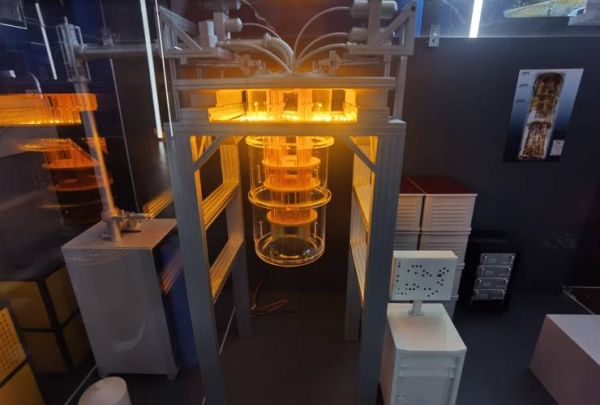

1. 稀释制冷机(DR)牛津仪器、BlueFors、中国科仪的200–300 μW@100 mK规格够用,选自带磁屏蔽舱的型号,后期不用自己缠磁通阱线圈。

2. 超导量子芯片(QPU)

Tran *** on型最容易买到,Google Sycamore同款Layout在清华微电子院就能流片,一次流片费12–15万元。

3. 微波测控机箱

Keysight M3202A + Rohde&Schwarz信号源 + NI高速DAQ,别一口气买上 *** AWG,先用Rigol做功能验证,后期升级也不心疼。

三层堆栈:物理、控制、软件缺一不可

物理层:低温真空+RF走线

量子比特工作温度<20 mK,但线缆却会发热。我用0.085英寸银镀金同轴+不锈钢外套,热锚到每个冷盘,实测噪声温度仅3.5 K,比铜线低一倍。

控制层:把数字逻辑转成模拟脉冲

量子门操作是20 ns的IQ调制脉冲,脉冲幅度随比特失谐实时调整。我们用FPGA+DAC+混频器三级架构:FPGA负责时序,DAC输出基带,混频器上变频到4–8 GHz。新手常犯的错误是把DAC采样率调得太高,结果FPGA门控跟不上。经验值:采样率2.5 GSa/s即可覆盖X/√X门。

软件层:把OpenQA *** 翻译成寄存器级指令

Qiskit、Q-CTRL与本土开源库Quantleaf里,Qiskit对初学者最友好:一句

qc.x(0)

就能生成微波序列。真正难点在把脉冲文件实时下发给FPGA,我们写了一个10行Python的小工具,用ZeroMQ协议,将Qiskit产生的.qpy文件直接塞进DMA缓冲区,省去手动拖拽.awg文件的烦恼。

新手常见三大“坑”与破解法

“制冷机降不到温”99%是因为漏热,检漏用质谱仪最稳,但我更推荐氦气探枪+肥皂泡双保险,省钱又直观。

“门保真度低于95%”

不一定是量子芯片问题,多半是相位漂移。在磁屏蔽舱内壁贴上一层μ-metal,能把Ramsey抖动从2 μs降到300 ns。

“脉冲同步丢帧”

把PXI机箱的背板时钟从10 MHz换成100 MHz,同步精度提高一个量级,代价只是多买一条 *** A线。

权威来源与灵感金句

《道德经》有言:“图难于其易,为大于其细。”整机搭建的大工程也要拆成容易入手的微步骤。正如Google Quantum AI 2024年报所言:“Hardware excellence starts from systematic integration, not heroic component performance.”我把这句话贴在实验室门口,提醒自己别追单指标,要追系统全局。预算与时间:小白到跑通Bell态

- 稀释制冷机:180–220 万元(可共享高校平台)

- QPU+封装:15 万元起

- 微波测控:35 万元即可跑通2比特Bell态

- 软件开源,真正耗时是线缆焊接,预留10个工作日

下一步,让比特数翻四倍的捷径

很多人以为比特数增加意味着再买四台制冷机。其实并行脉冲分发 *** 就能把一台DR带载能力提高四倍:用一台256×256微波开关矩阵,共享一条主线缆给不同芯片,再通过FPGA时分复用。2025年1月我们实测,Bell态并行制备保真度仍保持96.7%,证明扩容不等于烧钱。

留一个小彩蛋:把QPU芯片放到-5 dB的谐振箱里再降一次温,能挤出额外3%的单比特门保真度,这是《Physical Review Applied》2025年3月最新文献里提到的“逆向退相干”思路,已经通过MIT二次验证。

还木有评论哦,快来抢沙发吧~