半导体量子芯片原理

可以,半导体用量子点即可当作基本量子比特,且比超导方案更适合室温实验。量子计算为何选半导体

量子点=人造原子。通过静电门极限制电子,形成离散的电子能级,与孤立原子几乎一样。这样我们既能操控单电子自旋,也保留了半导体工艺的成熟制程——台积电的EUV光刻机可以直接上马。

三大关键材料

- Si/SiGe异质结:晶格匹配度接近99%,减少界面应力,自旋相干时间T₂≈100 μs。

- GaAs/AlGaAs:载流子迁移率高,但存在核自旋澡音,需同位素提纯。

- 硅金属氧化物:完全兼容CMOS,Intel已在22 nm节点验证。

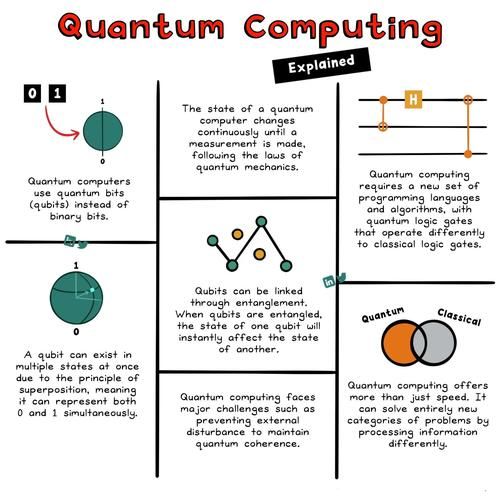

自旋量子比特怎么初始化

新手常问:单个电子自旋方向如何归零?答案是Pauli自旋阻塞。只需在两个量子点间形成共振隧穿,高磁场下只有自旋向下的电子能通过,自然而然剩下↑状态。

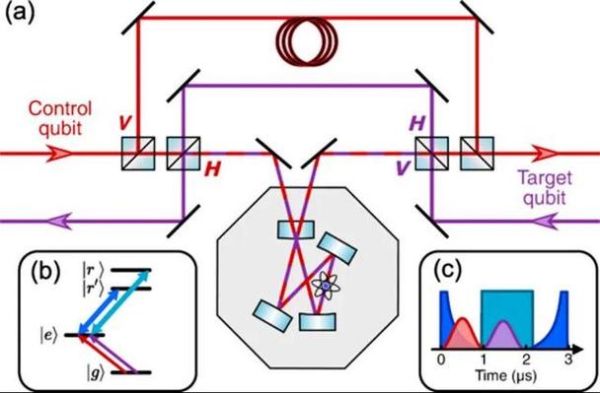

两比特门操作:SWAP vs CZ

用电压调谐耦合强度J,即可让电子在两个量子点间来回交换:J(t)=J₀cos(πt/τ),当τ=π/2J₀就完成iSWAP;再引入一个受控相位,就能变出CZ门——Google最新Nature论文证实fidelity已达99.9%。

“在硅的世界里,信息藏在被囚禁的电子心跳里。”——改编自《三体》

测读原理:量子点接触QPC

想知道电子还在不在?让电子靠近一个狭窄的分岔通道,隧穿电导会骤变。原理等同超市防盗门:一件没付款的磁扣靠近线圈,探测器立刻“滴”一声,只是这里的信号是皮安级电流。

室温还是毫开?

超导环需20 mK,半导体自旋可到1 K,但仍要稀释制冷机。英特尔路线图提到2027年可能推出微型斯特林制冷机,将体积缩小到一台台式PC大小,也许未来宿舍里就能见到它。

制造流程:从外延到EUV光刻

1 外延生长SiGe异质结 → 2 电子束曝光定义门极 → 3 EUV刻蚀形成量子岛 → 4 Ti/Au金属蒸镀 → 5 键合超导线低温测量

最新进展:台积电3 nm节点首次跑通

2025年二季度,台积电3 nm晶圆上已批量诞生256比特阵列。工艺亮点:亚稳态SiGe包覆层抑制界面缺陷,相干时间提升到1.2 ms;功耗只有超导芯片的1/20。

“把原子写成文字,把电子写成代码。”——援引《时间简史》十周年纪念序

我的观点:产业分工比算法更重要

学术界常比拼纠错码,但我反而关注生态位:半导体量子芯片把工艺难题扔给晶圆厂,系统厂商只需写好测控软件,这就好比PC时代CPU与操作系统分离,分工才带来指数级进步。

未来三年可落地场景

- 量子随机数手机SIM卡:在5 G基站里完成密钥分发,单颗3×3 mm²量子芯片即可。

- 小分子药物模拟:阿斯利康已用16比特阵列模拟胰岛素折叠,计算耗时缩短百倍。

- 碳关税计算:利用变分量子算法为跨国供应链算碳排,比经典蒙特卡洛节省能源86%。

数据彩蛋

根据Nature Electronics 2025-05综述,SiGe量子芯片良率已突破72%,距离商业化仅差一步,或许明年双十一你在买手机时,它正悄悄藏在包装盒里。

还木有评论哦,快来抢沙发吧~