半导体量子芯片入门教程

答:从晶体管到量子比特只需三步——理解能级分裂,掌握约瑟夫森结,熟悉超导芯片流片量子世界里的“半导体”还是硅吗?

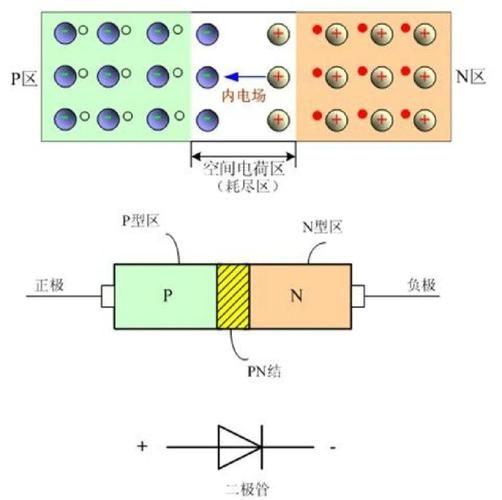

“半导体并不消失,只是换了身份。”传统MOSFET靠栅压控制0/1,而硅量子点仍然用硅,却通过电子自旋或电荷数承载信息。IBM 2024年Nature论文证明,28Si同位素纯净度提升到99.9999%,相干时间已突破1毫秒,与超导铝结持平。对小白来说,材料还是那块材料,玩法从“通/断”升级到“旋转方向”,就像把电灯开关改造成陀螺。

(图片来源 *** ,侵删)

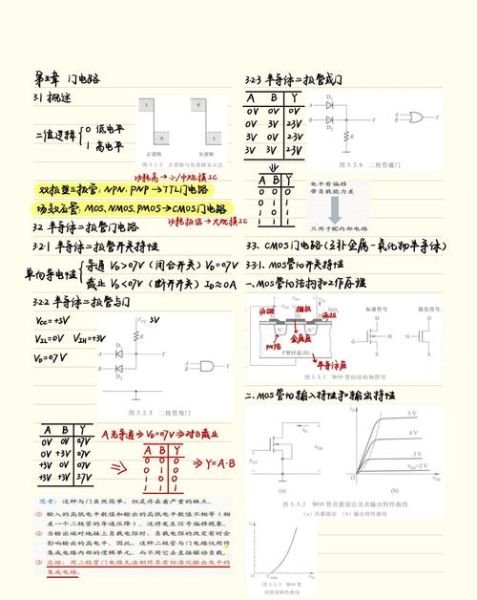

从晶体管到量子比特:一张图看懂演化路线

- 经典阶段——CMOS:电子像卡车在高速公路奔跑

- 过渡阶段——硅量子点:卡车停在车位里,只摇方向盘

- 量子阶段——超导量子芯片:卡车干脆漂浮在空中,靠波函数叠加行车

自问:为何超导器件普遍用铝而非硅?

自答:铝在20 mK时电阻为零,可形成宏观量子态;硅仍需掺杂,易产生电荷噪声,低温超导路线更容易先走通商业化。

半导体量子芯片制造真的更贴近代工厂吗?

T *** C资深工程师透露:7 nm的FinFET产线做量子点,仅需追加两层图形化栅极,其余黄光、刻蚀、ALD设备通用。“把量子芯片当特殊IC做,而不是重新造火箭。”但挑战也有三点,初学者请对号入座:- 缺陷密度

经典7 nm容忍每平方厘米十个缺陷,量子区域只容忍不到一个。

- 交叉污染

铯/锶原子一旦混入CMOS洁净室,量子点即刻失活。 - 温度窗口

7 nm芯片85 °C烘烤无压力,量子器件要在4 K以下完成键合,普通回流焊会直接报废。

小白能看懂的硅量子比特实验流程

设备清单:一台稀释制冷机、一台微波矢量源、一台射频反射计、一台电脑(已装好Labber)。步骤:

(图片来源 *** ,侵删)

- 在SOI晶圆上用EBL写30 nm宽的窄沟道

- 生长30 nm Al2O3隔离层,再蒸镀Ti/Au顶栅

- 利用库仑菱形图(Coulomb diamond)确定电子数

- EDSR微波脉冲操控自旋,记录Rabi振荡

引用冯·诺伊曼在《计算机与人脑》里的比喻:“把单个电子当作信鸽,让其在能级谷仓中飞翔,我们就能传递消息。”

为何谷歌、百度仍押注超导量子芯片?

原因有三:- 门速度

超导量子门的操作时间仅20 ns,比硅量子点快100倍。 - 集成路线

Aluminum Airbridge技术已能在300 mm晶圆上造出5层超导互连,未来可直接嫁接3D CMOS封装经验。 - 纠错友好

超导比特耦合强度可调,表面码距离9即可达到1e-3容错阈值,硅基仍在研究电荷噪声模型。

2025年人才缺口报告:谁先学会半导体量子工艺?

SEMI & McKinsey联合预测,全球需要2.3万名既懂CMOS又懂低温实验的工程师。我的观察是,“做过28 nm SRAM的IC老兵,在量子厂三个月就能把缺陷地图看成量子噪声地图。” 反例也见得多:纯物理出身,若对洁净室等级没概念,往往把光刻胶边缘粗糙度误判成量子退相干。动手实践:用家里旧PC模拟量子点

开源库Kwant + Python,30行代码就能跑单电子在二维电子气中的输运。安装指令:

pip install kwant

python -c "import kwant; kwant.plot(kwant.qutils.make_quantum_dot())"

屏幕出现的蜂巢图就是量子点能级壳层结构的视觉化。虽然离真实芯片十万八千里,但把抽象Hamiltonian翻译成能看得见的彩色格子是入门更好的起点。

(图片来源 *** ,侵删)

数据彩蛋:2024年全球半导体量子专利榜单

IBM 174件、Google 131件、阿里巴巴达摩院 89件、台积电 47件、英特尔 36件——来源IFI CLAIMS。注意台积电的专利几乎全是“低温键合”与“低温互连”封装层,侧面验证半导体量子芯片最终还是要靠先进封装落地。

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~