超导量子计算纠错码入门

是为什么超导量子计算必须谈“纠错”

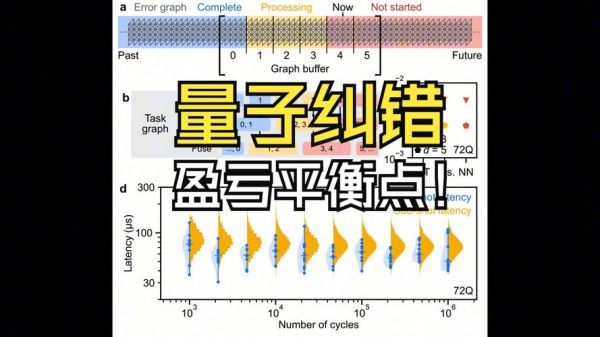

超导量子比特虽然速度高,但退相干时间短,“秒级”寿命内就出现大量位翻转。没有纠错,任何实用量子程序都会因噪声变成一团乱码。

(图片来源 *** ,侵删)

什么叫量子纠错码

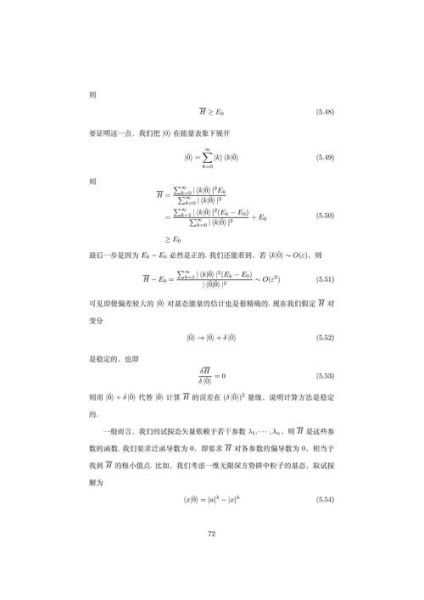

量子纠错码是给脆弱量子信息买保险:用多个物理比特“拼”成一个逻辑比特;只要错误数量低于阈值,逻辑比特就保持“零误码”。经典三重复码只能纠正0/1翻错,而量子必须同时处理:

- 位翻转(X错误)

- 相位翻转(Z错误)

- X+Z的组合错误

所以量子码必须更巧妙。

超导圈子更流行的三种纠错方案

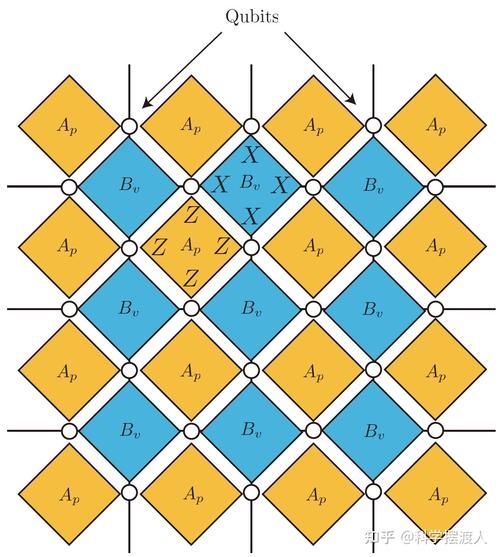

1. 表面码(Surface Code)

谷歌、IBM 实验机都用它。规则简单:- 把物理比特排成二维网格,每个量子比特只跟邻居纠缠。

- 周期性地测量“辅助位”,观察错误“症状”,而不是直接读逻辑比特。

- 门槛值约1%:目前超导设备单门错误已降到0.1%以内,所以理论上可行。

谷歌2023年在70比特Sycamore处理器上首次演示了表面码的β版本,逻辑错误率较裸比特降低10倍。

2. Bacon-Shor 码

适合长链式超导架构。优势:- 完全基于两比特门即可实现测量,硬件层布线更友好。

- 缺点:需要更多物理比特才能压制到相同逻辑错误率。

3. 色码(Color Code)

六角格架构的宠儿。亮点:同一个测量轮次就能同时探知X和Z错误,从而减少测量时间;但门图样比表面码复杂,实时解码器压力更大。新手常见疑惑:这些码到底差在哪儿?

自问:码率越高越好吗?自答:不是。表面码用1000个物理比特才编出1个逻辑比特,看似浪费,但物理错误足够低后,指数级抑制噪声,反而是最“经济”的方案。

(图片来源 *** ,侵删)

自问:那直接用更高效的LDPC量子码不就行了?

自答:LDPC需要“长程连线”,超导芯片目前仍是2D平面+近邻耦合,长程门会让错误率反升。谷歌2023年测试表明,在超导平台,表面码仍比LDPC稳定两个量级。

硬件与算法的闭环实验

2025年春,IBM Heron 处理器升级了可调耦合器,让CZ门错误率首次跌到0.05%。团队跑表面码d=5方案,连续观察5小时仅出现7次逻辑位翻转。这意味着,过去只存在于论文中的“实时纠错”已进入小时级运行时代。“我们把表面码的实时解码搬到CPU+GPU混合架构,延迟降到280 ns,远低于量子比特退相干时间。”——IBM量子负责人J. Gambetta

如何亲手“体验”一次表面码

工具链推荐(对小白零门槛):- qiskit-experiments:最新已集成d=3、5、7表面码生成语句。

- Stim:Google开源的高速采样器,一行代码就能注入翻转噪声。

- PyMatching:解码器,输入错误症状,直接输出应纠正的位置。

亲手跑通后,你会直观看到:当物理错误率<1%时,逻辑错误随码距d呈指数下降,这就是“阈值”魔法。

未来五年,门槛值会降到0.1%以下吗

我个人的观察是:不太可能,也没必要。超导材料极限摆在那里,更重要的是“控制电子学整体延迟”。当控制指令比量子比特寿命更快,我们就能在1%门槛附近用表面码持续扩张逻辑规模。正如狄更斯在《双城记》中写道:“这是一个最坏的时代,也是一个更好的时代。”低门槛虽遥不可及,但现在的0.1%门错误已经足够让量子计算走向应用。先飞起来,再换引擎。未来,我们或许会看到晶圆级超导芯片与实时解码专用ASIC一起封装,逻辑比特数量突破百万。那时候,“量子云”才会真正变成像今天的云计算一样触手可及。

(图片来源 *** ,侵删)

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~