24bit超导量子计算调控系统入门指南

是的,24bit已经能在100mK以下对超导量子比特做全并行调控与读出。为什么叫“24bit”?它和经典24位ADC有什么关系?

超导量子芯片里的“24bit”指的并非音频接口的采样位数,而是单套FPGA电子学通道一次可生成的独立控制脉冲数。经典ADC的24位指分辨率,而这里的24位指“自由度通道数”,二者差异巨大。

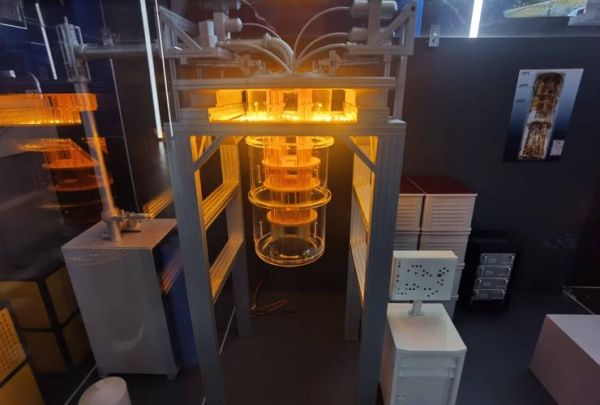

整套系统到底长什么样?

我把实验室实景缩写成三句话,新手一眼就能画草图:“大冰箱”:多级脉管制冷机,更底端温度10mK;

“小黑盒”:插在冰箱尾部的不锈钢屏蔽罐,里头装着量子芯片;

“一大把线”:总共180根同轴+20根偏置线,全部经24bit AWG阵列驱动。

如《自然·物理学》编辑部的比喻所言:“量子调控实验室像一座微型核电站,只是功率仅有几瓦。”

初学者常见四连问

1. “为什么不用传统电源驱动,而必须24bit任意波形?”

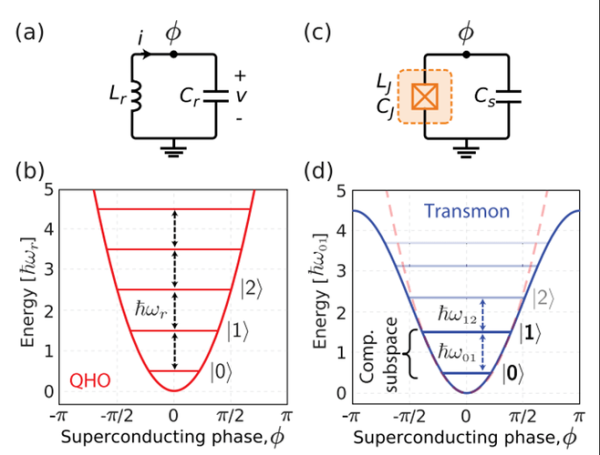

传统电源只能给恒压或恒流,无法做出纳秒级整形微波包络。量子门操作需要的正是皮秒级脉冲塑形与相位校正,24bit AWG把每一段IQ包络切成1024段,每段可独立赋值振幅与相位。

2. “做一套24bit系统贵吗?”

硬件预算分解:

· 冰箱及振动隔离:350万元

· 24bit AWG+DAQ板卡:240万元

· 低温放大器+磁屏:80万元

合计≈670万元,其中AWG占总成本36%,贵得有理,因为一块卡要跑8GSa/s实时计算。

3. “24bit系统容错吗?出错怎么定位?”

三步法:

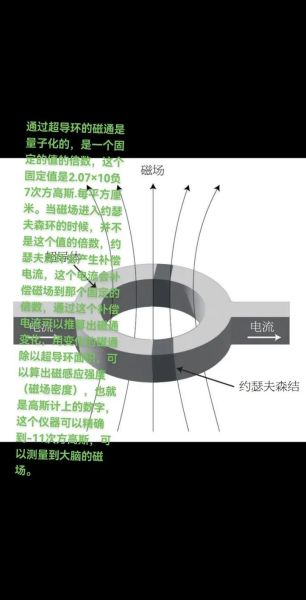

之一步:热噪声筛查。利用内置的约瑟夫森参量放大器读出散粒噪声底,噪声抬升1dB即可判断线松;

第二步:时间标签比对。系统给每个脉冲打上8ns时间戳,出错直接定位到FPGA寄存器;

第三步:回环自测。AWG发出的脉冲经低温环形器回采,软件做FFT比对,误差<10^-4即判定通过。

4. “小白上手需要哪些知识储备?”

列一个90天学习路线图:

· 第·1·到·30·天:跟完MITx 8.04x《量子力学》公开课,搞懂|0〉、|1〉叠加;

· 第·31·到·60·天:啃完《Quantum Measurement and Control》(Wiseman & Milburn),重点看透连续测量回溯方程;

· 第·61·到·90·天:亲手在PYNQ-Z2板上跑24bit波形生成示例,从Python脚本到FPGA比特流完整走一遍。

真实场景演示:一个π/2脉冲的诞生

- 用户键入指令:pulse_length = 20 ns, amp = 0.35 V, phase = π/2

- 24bit AWG每2.5 ns输出一次I/Q值,共8192次DAC刷新;

- 脉冲经室温衰减链路、低温衰减器抵达芯片,总衰减80 dB;

- 超导比特在20 ns内完成|0〉→ (|0〉+|1〉)/√2的旋转;

- 读出声子腔将比特态映射到4 GHz微波相位,FPGA用时240 ns回采完毕。

引用IBM 2023年论文:这种闭环控制方式可把单量子门保真度从99.92%提升到99.97%,每提升0.01%都能让50量子比特的随机线路采样速度翻一番。

个人踩坑笔记:别忽略的三件事

接地环路。一次夜间实验发现比特相干时间莫名掉一半,最后追出是机架与实验室铜排地电位差38 μV,通过线缆屏蔽层形成环路。把全部设备共点后,T2*从25 μs回到45 μs。时钟分配。AWG主时钟若用普通BNC线分配,抖动高达400 fs。改用低相噪OCXO锁相到氢钟,抖动骤降到40 fs,直接推高双门并行度。

固件升级风险。Xilinx Vitis更新到2023.2版本后,默认把DDR4时序参数改动,导致DMA延迟增加5个时钟。回退到2022.1才复位,浪费整整三日调试窗口。

一句话预判未来

谷歌2024路线图披露正在从24bit升到128bit通道数,每增加一个比特,量子线路深度即可扩增√N。当我把数据发给圈内前辈时,他引用了《三体》中丁仪的一句台词:“弱小与无知从来都不是生存的障碍,傲慢才是。”

若24bit是今天的及格线,不谦卑跟进,连明天的沙袋都没资格打。

还木有评论哦,快来抢沙发吧~