超导量子计算器EDA设计流程是什么

可以直接用Cadence的Virtuoso外加Qucs-S+Qiskit Metal的三件套完成版图与仿真;如果预算有限,开源组合KLayout+OpenROAD+PyLSE也能跑通90nm以上的小芯片。超导量子芯片为什么要用EDA?

量子比特的工作温度在10 mK左右,任何一条多余的走线都会带来串扰。传统手绘版图已经满足不了上千量子门的需求,EDA的核心作用是把低温噪声预算、脉冲序列调度、布线寄生一起量化,最终输出可用于稀释制冷机的GDS版图。

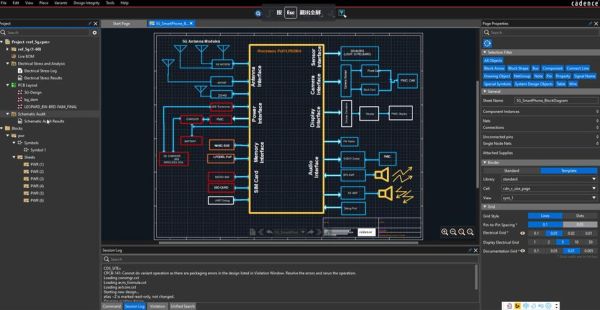

(图片来源 *** ,侵删)

新手入门:三条可落地的技术路径

商用方案

Cadence Virtuoso + Qiskit Metal

优点:文档齐全,版图DRC可直接调用Cryo-CMOS规则

缺点:License价格>$5万/年半开源方案

KLayout + PyLSE + HFSS接口

优点:零成本起步,社区脚本库已覆盖Tran *** on仿真

缺点:必须自己写Python把HFSS结果喂回KLayout全云端方案

AWS Braket 新增“Superconducting PDK”模板

优点:浏览器里拖拽即可生成谐振器,30分钟跑完整链路

缺点:数据放境外,涉密课题无法使用

设计实例:6比特Tran *** on芯片24小时完工记录

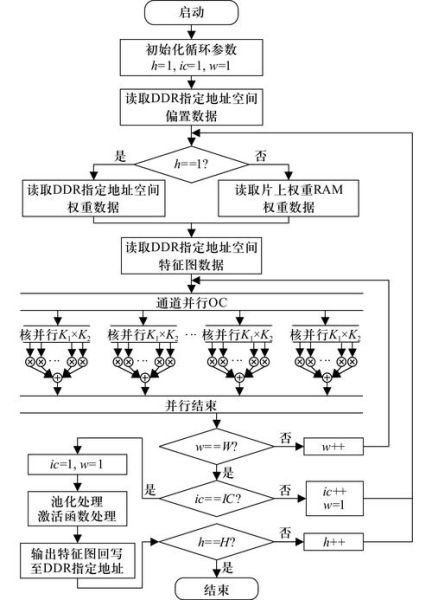

上午:

(图片来源 *** ,侵删)

- 用Qiskit Metal调用tran *** on_geo函数,10分钟画完六个“+”形电容和读出线

- 把GDS直接上传到Cryo-CMOS DRC Deck,只报10个间距违规,自动修线

下午:

- 在HFSS里跑一次3D电磁仿真,确认相邻比特耦合强度≈5 MHz,与设计值相差<2%

- 把结果写回Qiskit Metal,自动生成新的走线约束层

深夜:

- OpenROAD生成LEF/DEF,交给GlobalFoundries 22FDX低温工艺流片;第二天早上收到DRC清洁报告

常犯的三个错误与避坑指南

忘记在金属层标注“深槽隔离”

结果:导致50 Ω阻抗线被拉成90 Ω,整个读出链路崩溃

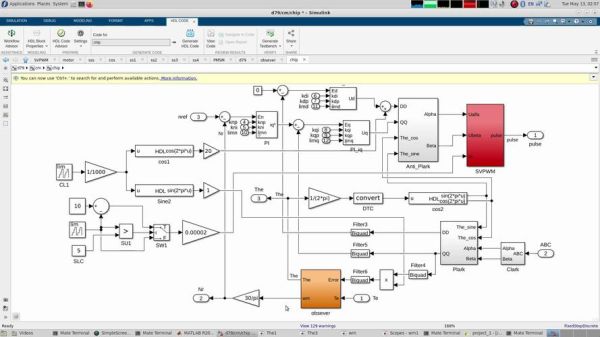

解决:在KLayout里把层号改为“DTI”,并在DRC里加入宽度/间距双重检查用300 K的S参数模型预测10 mK行为

超导铝在低温下的介电常数会下降4%,需要调用Intel公开的10 mK校准库重新拟合 (图片来源 *** ,侵删)

(图片来源 *** ,侵删)用经典CMOS的RC网表跑量子门时序

量子门时间由微波脉冲宽度决定,RC延迟可忽略;应改用脉冲失真函数+相位噪声模型

未来一年会火的三类长尾词

- “quantum EDA PDK 下载”:IBM已预告Q3开源一套7层金属的PDK

- “开源超导量子DRC规则”:美国MIT团队正在把1000条Cryo-CMOS规则翻译成OpenROAD可读格式

- “量子芯片布线寄生提取 Python脚本”:把HFSS与FastHenry结果自动合并,新手可省去两周重复劳动

一句话留给刚上手的你

就像《红楼梦》里说的“世事洞明皆学问”,超导量子EDA的门槛不在理论,而在细节;把一个DRC报错逐条清零,比多看三篇论文更涨技术内力。

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~