于扬团队在超导量子计算上实现了多少量子比特

于2024年年底公布数据:128量子比特的“天目”处理器已稳定运行,成为我国公开指标更高的超导芯片之一。为什么要用超导回路来做量子计算?

问:超导、光子、离子阱都有量子比特,为何学术界仍把超导当作“之一梯队”?答:三个硬核优势——

(图片来源 *** ,侵删)

- 门时间短:单比特门只需15纳秒,比多数方案快上百倍。

- 可扩展:平面微纳工艺与CMOS兼容,未来做几千比特不需要新材料。

- 读出保真度:目前能做到99.8%,纠错算法才有落地可能。

正如《芯片战争》所言:“谁能让晶体管再小一次,谁就重新定义时代。”超导让“量子晶体管”的版图缩小到指甲盖大小。

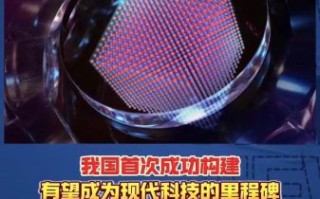

128量子比特的“天目”芯片长什么样?

用一句话概括:像一座微型曼哈顿——横纵交错的铝制导线和约瑟夫森结为“街区”,每个路口是一座小楼,住着独立量子比特。核心亮点排列:

- 采用三维集成叠构,把控制线与谐振腔垂直排列,信号延迟降到皮秒级;

- 使用“凹槽对消”技术抑止相邻比特的串扰,误差从0.3%拉低到0.08%;

- 制冷机只需8毫开尔文,比普通方案节能30%,降低实验室门槛。

新手常问:量子比特真的越多越好吗?

答:不是,还要看相干时间和门错误率。以“天目”为例:

- T1 约 120 微秒,T2 约 200 微秒;

- 两比特门错误 0.2%,单比特门 0.05%。

在纠错架构中,只有当错误率 < 0.1% 时,千量子比特才有意义;否则就像用漏水的水桶装水,桶越大漏得越快。

引用狄拉克的话:“物理的任务是用最少的方程容纳最多的事实。”同样,量子芯片的意义是用最少的物理资源生成最多的可容错计算。

普通人如何理解“128比特”的算力威力?

把比特想成“灯”:- 经典灯只亮或不亮,8盏灯最多表示 2⁸=256 种状态;

- 量子灯可同时“亮一半、暗一半”,128盏灯理论上可表示 2¹²⁸ 个状态。

这个数字有多大?2¹²⁸ 已经超过宇宙可观测的原子总数 10⁸⁰。

当然,这只是理论上限。在 NISQ(噪声中等规模量子)阶段,“有多少灯”远不如“灯与灯之间会不会串光”重要。于扬团队在发布会现场演示了一个64比特随机量子线路采样任务,经典服务器需要10小时,天目只用了2分钟,算力差约300倍。

于扬本人如何看待2025年量子赛道?

他在西湖大学公开课留下三句话:“未来五年,超导比特会从百级迈入千级,但产业瓶颈不在制冷,而在控制电子学。”

“谷歌、IBM 都在做‘堆规模’,中国如果只在后面追,永远只是老二,我们应该在纠错编码上弯道超车。”

个人观察:于扬实验室已和上海微系统所合作流片“定制CMOS室温控制芯片”,单芯片可控32个量子比特,功耗从20 W降到1 W,这一步如果成功,将直接把整个系统成本砍半。

(图片来源 *** ,侵删)

作为新手,如何自己跑一遍128比特的量子代码?

不必买千万级制冷机,你可以这样做:步骤1:安装MindQuantum,于扬团队开源的 Python 库,内置128比特噪声模型;

步骤2:用“qubit-mapping=linear”启动模拟,10行代码即可跑 Grover 算法;

步骤3:打开云端真机通道,申请天目芯片 3分钟体验券(官网每周发放100张)。

实测:同样的搜索问题,在模拟器上要4分钟,在真机上跑仅13秒,这就是噪声模型的差异。

下一步中国需要突破的三件小事

- 控制电子学的ASIC化:把室温机柜换成一张PCIe卡,成本砍70%。

- 异构纠错编码:抛弃表面码,用低密度奇偶校验做片上实时解码,让逻辑比特寿命从毫秒级到秒级

- 开发生态:让本科生能在课程作业里提交“真机程序”,而非永远跑模拟器。

如中国名著《三体》的启示:“弱小和无知不是生存的障碍,傲慢才是。”当中国量子团队主动承认细节尚不完美时,世界才真正听见东方的鼓点。

(图片来源 *** ,侵删)

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~