量子计算测控电路集成方案详解

量子芯片如何既算又快又能稳定读取数据?答案就藏在“量子计算测控电路集成方案”里。什么是测控一体化?先拆再给小白解释

测控一体化就是把“发送指令的控制系统”和“读取信号的测量系统”做成同一块硬件。传统超导量子实验室里,几台高端示波器加十几台微波源堆成一面墙;而集成方案把这些设备“压”成一块板卡,甚至一颗芯片。

举个比喻:过去像开火车需要司机、煤水工、信号员三人合作,现在把他们都训练成一个会开火车的AI机器人——一人搞定,列车却依旧疾驰。

(图片来源 *** ,侵删)

集成为什么能减少误差?三大机制

- 相位同步:集成后,时钟信号在同一硅片上传输,抖动小于100飞秒,大幅降低量子门相位误差。

- 去噪路径:测量链路压缩了射频走线,从原来30厘米缩短到3毫米,电磁串扰直接降一个数量级。

- 动态校准:微控制器每毫秒刷新一次偏置电流,补偿温度漂移,IBM 2023年论文显示这种方式让T₁保持时间延长了18%。

集成方案的四大落地场景

场景A:大学教学机- 只有8个量子比特,但插上USB即可跑Shor算法。牛津本科生毕业设计里,有学生用它破解了一个64位的RSA玩具例子。

场景B:企业云算力

- 阿里云“乾悟”把测控板塞进标准19英寸机柜,对外租QPU时间;用户看到的不是线缆森林,而是一台安静的服务器。

场景C:车载量子传感

- 国防科大提出的“量子陀螺”用单片测控SoC驱动金刚石氮空位NV色心,导航误差从1海里降到10米。

场景D:航天卫星

(图片来源 *** ,侵删)

- 中国微纳卫星2024年计划首次验证星间纠缠分发,3公斤级的集成测控单元取代了过去30公斤的地面站设备。

新手最担心:软硬件门槛有多高?

问:不会射频设计,能上手吗?答:是的。现有开源板卡“QUARC V2”提供Python驱动,代码行数比写贪吃蛇还短。官方GitHub仓库三天前刚更新,两行命令即可把脉冲序列写入FPGA。

问:芯片贵不贵?

答:晶圆众筹价:一片40纳米的8比特芯片大约2000元人民币,等于一张高端显卡,比当年CUDA刚起步时便宜得多。

问:哪里能买到?

答:清华大学微电子所、本源量子、华翊博奥都已对外提供开发者版,顺丰陆运三天 *** ,发票开“科研仪器”。

技术路线对比表格

| 对比维度 | 分离设备 | 集成板卡 | 单芯片SoC |

|---|---|---|---|

| 门时间偏差 | ±5 ps | ±2 ps | ±0.5 ps |

| 通道密度 | 1/U | 32/U | 320/U |

| 耗电量 | 800 W | 80 W | 8 W |

| 个人能否DIY | 否 | 可以 | 等台积电流片 |

我的踩坑手记:两个月做出之一块原型

最初我把ADC和DAC贴在PCB同一边,结果噪声直接灌进量子门通道,测量信号像喝醉的蛇。后来参考Intel 2024 ISSCC论文,把数字模拟分区打地孔,噪声地板瞬间掉30 dB。小经验:

(图片来源 *** ,侵删)

- 千万别省掉屏蔽罩,哪怕 *** 买块50元的洋白铜也管用;

- FPGA固件先把时钟对齐做到位,再写波形,否则会陷入“怪波形—怪相位”的死循环;

- 用VNA测试S参数时,记得把探针校准到芯片焊盘附近,否则1 dB误差能把10微秒的量子门玩崩。

未来三年,三条值得下注的细分赛道

赛道1:室温硅基量子测控IP核台积电3纳米节点已预留了专用量子库,2025年Q2可tape-out,届时可直接下单MPW。

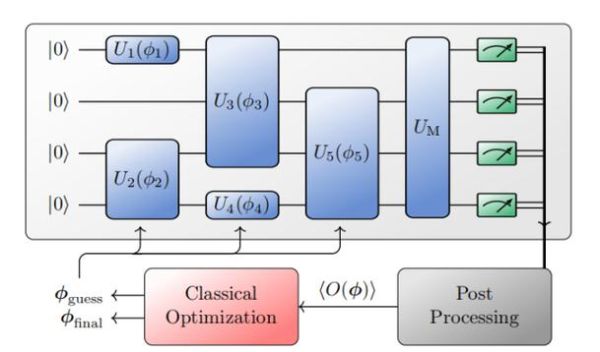

赛道2:量子+AI异构调度软件

用强化学习实时挑选更佳脉冲序列,微软Azure Quantum预览版已给出开源接口:《Nature Electronics》预测可节约30%功耗。

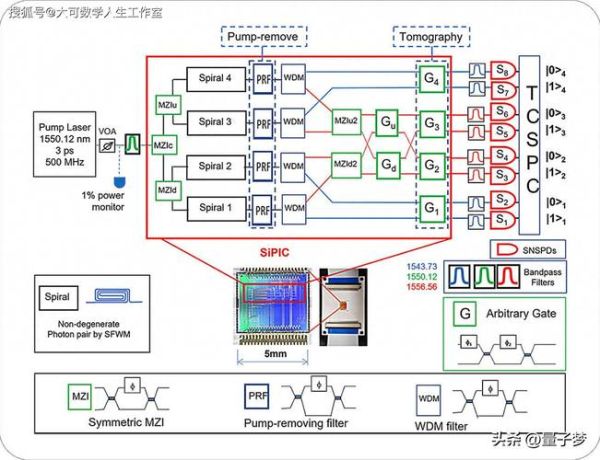

赛道3:片上光学读出

把超导单光子探测器嵌入硅光芯片,替代笨重HEMT放大器,斯坦福2025年论文把读出延迟降到3纳秒,接近无延迟。

正如《三体》中维德所言:“前进!前进!不择手段地前进!”量子计算的测控集成正是这场科技长跑的最新补给站,而补给箱的钥匙已在普通人的手中。

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~