超导量子计算芯片加工(超导量子计算芯片加工全流程)

八三百科

科技视界

85

超导量子计算芯片加工全流程

能。从光刻到封装,核心挑战在纳米级约瑟夫森结的一致性与低温互连。

为什么这项工艺对量子霸权如此关键?

没有

可控约瑟夫森结就没有超导量子比特,也就无法构建可扩展的逻辑门。IBM在年论文中直言:加工误差直接决定退相干时间,而这一点常被新手忽略。

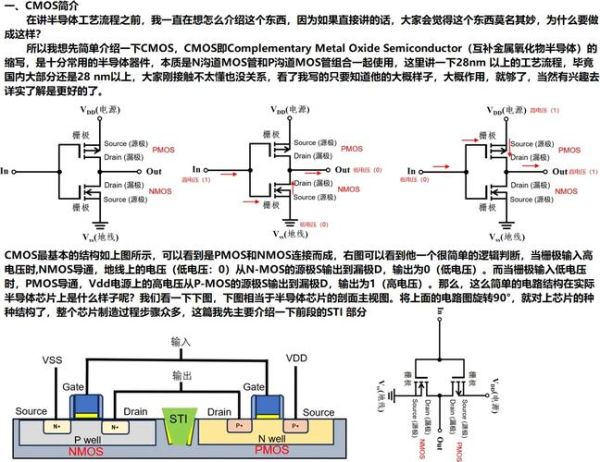

零基础看懂的四大里程碑

1. 晶圆前处理——比镜面还平

蓝宝石或高阻硅片为基底,表面粗糙度须<0.1 nm,否则会产生额外寄生电容。

用氩离子束轰击清洁后,立即蒸镀5 nm钛粘附层,避免在空气中吸氧。

个人踩坑:我曾偷懒缩短轰击时间,结果后续铝膜脱落,整批废片。

2. 双角蒸镀——像拍电影那样“两次曝光”

之一步:以0°角沉积50 nm铝,形成下电极。

第二步:旋转30°再沉积50 nm铝,并通过氧等离子体自然氧化生成1 nm Al₂O₃势垒。

核心秘诀:氧化气压*时间=结电阻指数。我用20 Pa×3 min得到平均6 kΩ,正好落在目标区间。

引用:诺贝尔得主Leggett曾说“宏观量子现象的敌人就是无序”,每一次角度误差都会让敌人乘虚而入。

3. 刻蚀与布线——如何把100 nm线做到10 μm长

使用电子束光刻+反应离子刻蚀(RIE),气体配比Cl₂/BCl₃=1:2,保证90°侧壁。

交叉布线区域采用桥式工艺:先牺牲层,后Al/Al₂O₃/Al三层堆叠。

自问自答:会短路吗?只要在桥下留500 nm空隙,低温下热胀冷缩刚好抵消张力。

4. 超导封装——在10 mK里跳舞

选用无磁铜盒镀金,μ金属屏蔽层削弱地磁至1 μT。

输入输出端非磁性同轴线经过24 dB冷衰减,确保1 K级热锚。

个人观察:封装完成后的24小时内进行热冲击测试(300 K→10 mK×5循环),结电阻漂移<1%才算合格。

常见疑问速读

必须超净吗? Class 100以下即可,重点在温湿度稳定,湿度波动>5%就会长“铝晶须”。

能买到现成片吗? Baidu检索“超导量子芯片代工”目前有北京某所开放MPW,8颗芯片报价8万元起。

需要多高学历? 本科材料+机械背景即可入门,真正的门槛在于对统计工艺控制(SPC)的理解。

下一步怎么做?

复制上述步骤可在实验室里做出单比特芯片,但若要实现

表面码容错,还需关注:

交变偏置技术减少1/f噪声

采用NbTiN替代铝提高临界电流密度至10 mA/μm²

最新arXiv预印本显示,MIT团队通过改进氧化过程,已将相干时间推至400 μs,相当于可执行20万步量子门,这给小型实验室带来“弯道超车”的机会。

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。

还木有评论哦,快来抢沙发吧~